Toshiba en Japan Semiconductor ontwikkelen automatisch analoog proces

Het 0,13-micron-proces dat wordt toegepast op analoge ICS wordt beweerd een geoptimaliseerde combinatie van processen en apparaten te bieden, volgens nominale spanning, prestaties, betrouwbaarheid en kosten, voor analoge circuits voor auto's en ENVM op een enkele chip.

Analoge IC's, waaronder IC's van de motorrijder, worden gebruikt in een breed scala aan automotive -toepassingen. Met de overgang naar elektrische voertuigen en toename van voertuigen met ADAS, wordt de analoge IC -markt naar verwachting continue groei.

Dit heeft een vereiste gecreëerd voor een veelzijdig, speciaal automotive platform dat kan voldoen aan een breed scala aan vereisten met betrekking tot autotoepassingen.

Aangezien ENVM en een microcontroller -eenheid (MCU) niet zijn gerealiseerd op een enkele chip, is het totale IC -gebied groot.

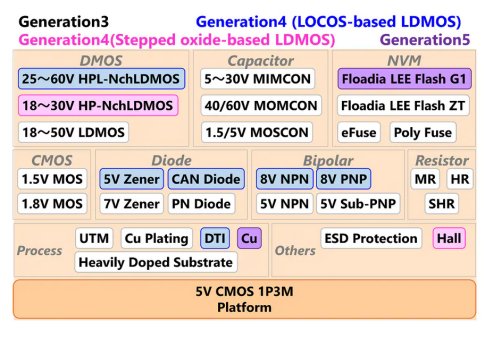

Toshiba en Japan Semiconductor bieden drie LDMOS -structuren en een zeer brede apparaatopstelling, inclusief ENVM, die selecteerbaar zijn om aan verschillende vereisten te voldoen.

Nu hebben ze ontwikkeld wat een zeer betrouwbaar proces is voor analoge IC's die voldoen aan AEC-Q100/Grade-0, een internationale standaard in de Automotive-betrouwbaarheid.

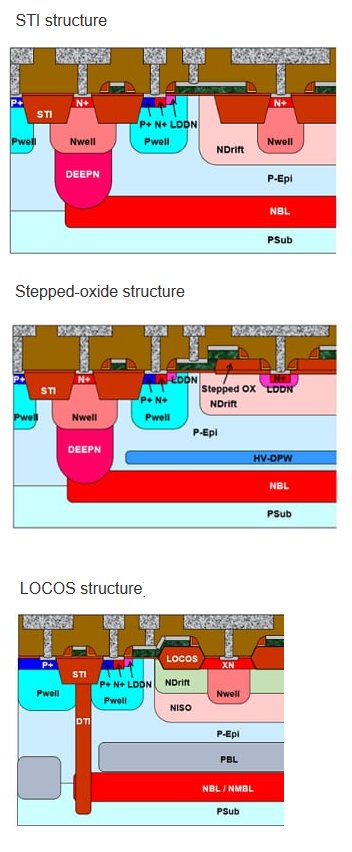

Er is een afweging geweest tussen on-resistentie (rAanA), een belangrijke parameter voor LDMO's en afbraakspanning tussen afvoer en bron (BVDSS).

Hoe lager de rAanA, hoe beter de prestaties met een constante bvDSS. Toshiba en Japan Semiconductor bevestigden dat twee soorten LDMO's, met getrapte oxide of locos tussen de afvoer en bron, een maximale r hebbenAanA dat is 44%*3 Beter dan op STI gebaseerde LDMO's.

Ze bepaalden ook mechanismen om de voordelen van LDMOS-apparaatbetrouwbaarheid, faalpercentages en ESD-tolerantie van LDMOS te evalueren.

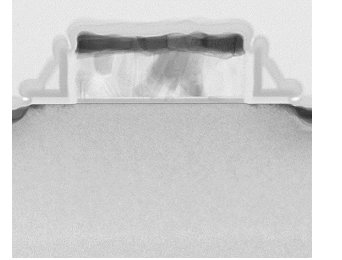

Envm van Floadia Corporation (Floadia Lee Flash G1) ingebed in het platform is voorzien van slechts drie extra maskers.

Ze kunnen voldoen aan de eisen van hoge betrouwbaarheid voor analoge stroomapparaten voor auto's zonder te beïnvloeden op basisplatforms en apparaten.

Ze vermijden ook mal-functie in de envm door de lay-out te optimaliseren om het te beschermen tegen de ruis veroorzaakt door het veranderen van LDMO's in de analoge circuits.

Toshiba en Japan Semiconductor zijn van plan om te beginnen met het bemonsteren van autoductoren van auto's met het nieuw ontwikkelde platform in december 2022.

LDMOS: laterale dubbele diffuse MOS (metaaloxide halfgeleider).

Locos: Lokale oxidatie van silicium. Gebruik siliciumnitride -film als een hard masker en maak selectief een siliciumoxidefilm op Si -substraat en isoleert elementen.

Toshiba en Japan Semiconductor bevestigden dat twee soorten LDMO's, met getrapte oxide of locos tussen de afvoer en bron, een maximale r hebbenAanA die 44% beter is dan op STI gebaseerde LDMO's, Toshiba-testresultaten.

STI: ondiepe trench isolatie. Isoleert elementen door isolatorfilm in ondiepe loopgraven in te bedden.

Apparaat line-up van het ontwikkelde platform

Structuren van de drie soorten LDMOS -structuur

Floadia's Envm TEM -afbeelding en het evaluatieresultaat van de uithoudingsvermogenstest en data retentietest (Toshiba -testresultaten)

(a) Envm TEM -afbeelding

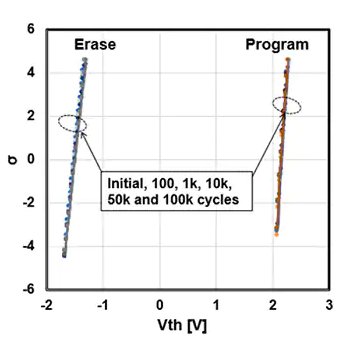

(b) Uitrustingstest

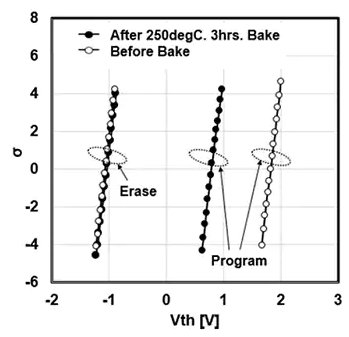

(c) Gegevensretentietest